# **Application Note**

# **AN\_386**

## FT600 Maximize Performance

Version 1.0

Issue Date: 2015-10-19

Data transfer through USB devices depends on many factors. This application note discusses how to optimize throughput by making use of FT600 and FT601 FIFO buffer.

Use of FTDI devices in life support and/or safety applications is entirely at the user's risk, and the user agrees to defend, indemnify and hold FTDI harmless from any and all damages, claims, suits or expense resulting from such use.

Unit 1, 2 Seaward Place, Glasgow G41 1HH, United Kingdom Tel.: +44 (0) 141 429 2777 Fax: + 44 (0) 141 429 2758

Web Site: <a href="http://ftdichip.com">http://ftdichip.com</a>

## **Table of Contents**

| 1              | FTD:    | I FT600 and FT601 USB 3.0 to FIFO Bridge                                         | 2  |

|----------------|---------|----------------------------------------------------------------------------------|----|

| 2              | FT60    | 00 and FT601 FIFO interface                                                      | 3  |

| 2              | 2.1 F   | FDI USB3.0 FIFO bridge throughput                                                | 3  |

|                | 2.1.1   | The performance of the application and the USB device driver                     | 3  |

| 2              | 2.2 F   | Γ601 data transfer performance demonstration setup .                             | 3  |

|                | 2.2.1   | Data transfer environment setup                                                  | 3  |

|                | 2.2.2   | FT600 and FT601 internal FIFO size and configuration                             | 4  |

|                | 2.2.3   | FIFO interface timing diagram                                                    | 5  |

|                | 2.2.4   | Optimize the application and FIFO master design to get the max data rate $\dots$ | 7  |

|                | 2.2.5   | FT601 data throughput demonstration                                              | 7  |

| 3              | Cond    | clusion                                                                          | 10 |

| 4              | Cont    | tact Information                                                                 | 11 |

| Α <sub>Ι</sub> | ppend   | lix A – References                                                               | 12 |

| ı              | Docum   | ent References                                                                   | 12 |

| 1              | Acrony  | ms and Abbreviations                                                             | 12 |

| Α <sub>Ι</sub> | pend    | lix B – List of Tables & Figures                                                 | 13 |

| ı              | List of | Tables                                                                           | 13 |

| I              | List of | Figures                                                                          | 13 |

| Αı             | pend    | lix C - Revision History                                                         | 14 |

## 1 FTDI FT600 and FT601 USB 3.0 to FIFO Bridge

FT600 and FT601 are FTDI USB 3.0 to FIFO interface bridge chips. The chips handle USB 3.0 protocol and transfer by themselves. The chips provide flexible configuration on the parallel interface, offering either single or multi-channel FIFO interfaces.

When designing with the FT600 and FT601, the user can focus on the data transfer between simple parallel interface rather than the USB 3.0 protocol. This greatly reduces the development time and effort.

#### 2 FT600 and FT601 FIFO interface

FTDI FT600 and FT601 provide 2 types of parallel FIFO interface, 600 and 245 modes. The 245 interface mode is similar to that which can be found on the FTDI FT232R and FT232H serial products. To cater for the higher data rate, FT600 and FT601 are synchronous parallel bus designs. FT600 and FT601 provide a 100 MHz reference clock to the FIFO master, the data word is presented at the FIFO interface back to back at 100 MHz clock in the FIFO bus transactions.

FTDI USB 3.0 bridge chips come with 2 chip packages targeted for different user requirements. The FT601 is designed for higher throughput with a 32 bit parallel data interface, the max FIFO throughput is 400 Mbytes/s. The FT600 is a design for small pin count with 16 bit parallel data interface, the max FIFO throughput is 200 Mbytes/s.

### 2.1 FTDI USB3.0 FIFO bridge throughput

Although the USB 3.0 specification has a line speed of 5 Gbps, in reality, the overall data transfer rate is the result of the combination on the performance of the PC hardware, the OS, the USB XHCI host, the USB host driver, the USB device driver, the application and the USB 3.0 device design.

In this document, we will not address the theoretical max data rate USB 3.0 can reach, but rather, we will take the FT601 data transfer demonstration as an example to illustrate the effective data throughput between the USB application and the FIFO master design, which is much more closer to the real implementation that users will do with the FT601.

In this document, we assume that the PC speed, the OS, the USB XHCI host and the XHCI host driver are well performing and the USB speed is 5 Gbps, above the FIFO interface at 3.2 Gbps max (400 Mbytes/s for FT601), we will evaluate performance contribution of the application, the USB device driver and FIFO master interface design. A dedicated section below describes design consideration of the FIFO master to improve the system throughput.

#### 2.1.1 The performance of the application and the USB device driver

FTDI delivers the D3XX driver for the FT600 and FT601 USB devices. The device driver is designed to handle the high data throughput, it supports the asynchronous overlapped the USB data transfer. This means the user's application can issue multiple data transfers to the D3XX driver. With this design, the gap between the data transfers are minimized and so data rate for a continuous data stream is improved.

The D3XX driver and FT600 design support continuous streaming data transfer. The application can setup the FT600 channels for one time, the USB data IN and OUT channels will be open for data streaming until a stop command is issued.

#### 2.2 FT601 data transfer performance demonstration setup

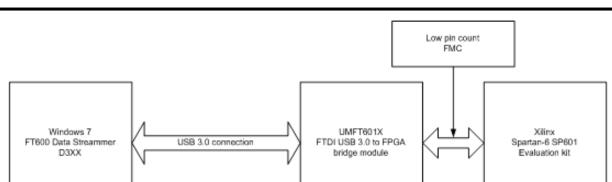

#### 2.2.1 Data transfer environment setup

The performance demonstration is based on FTDI data streaming application and a data source/sink FPGA design.

Windows version: Windows 7 SP1 x32, Lenovo ThinkCentre Edge, Intel® Core i7-3770, 3.4 GHz, 8 GB Memory.

Application: FTDI data streamer, driver D3xx version 1.0.0.5.

Hardware: UMFT601X module, Xilinx® Spartan-6 FPGA SP601 evaluation kit.

Figure 1 performance demo setup diagram

In this demonstration, the FPGA is designed so that it will read data from the OUT FIFO channel, whenever it is ready, and fill up the IN FIFO channel whenever it is empty.

The FTDI data streamer application will send out data to FT601 or read in data from FT601 once the test starts.

#### 2.2.2 FT600 and FT601 internal FIFO size and configuration

The FT600 and FT601 FIFO mode and the FIFO size configuration are listed in below.

| Mode           | Channel<br>number | FIFO size for each channel (double buffered) |  |

|----------------|-------------------|----------------------------------------------|--|

| 245            | 1 in and 1 out    | 4 KB                                         |  |

| FT600          | 1 in and 1 out    | 4 KB                                         |  |

| FT600          | 2 in and 2 out    | 2 KB                                         |  |

| FT600          | 4 in and 4 out    | 1 KB                                         |  |

| 245 IN only    | 1 in              | 8 KB                                         |  |

| 245 OUT only   | 1 out             | 8 KB                                         |  |

| FT600 IN only  | 1 in              | 8 KB                                         |  |

| FT600 OUT only | 1 out             | 8 KB                                         |  |

Table 1 FT600/FT601 mode configuration and FIFO size for each channel

In a high data rate application design, most of the time; the application will initiate a transfer which consists of multiple of USB packets. In this case, the FIFO master normally can read or fill up the FIFO in full FIFO size in one bus transactions. It happens that at the end of USB transfer, there will be a short packet that indicates the end of the current transfer.

To handle this scenario, the FT601 and FT600 design monitors the FIFO interface transaction, once the FIFO transaction stops, even before the FIFO is full or empty, the FT601 and FT600 will consider the data ready to process, and complete the current USB transfers.

For example, if the FT601 is configured in 1 channel, IN FIFO size is 4 KB, if the FIFO master writes 3 KB data to the IN FIFO and stops, the FT601 will get control of the current FIFO and

forward the data to USB interface. In the meantime, the FT601 will provide the next available FIFO to the FIFO master to fill up more data.

For the USB out transfer, it is recommended that the FIFO master should read out all the available data in the FIFO in one FIFO bus transaction.

#### 2.2.3 FIFO interface timing diagram

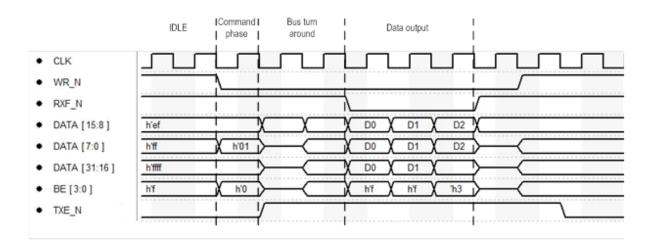

In the below example the FIFO interface timing diagram is used for FIFO bus efficiency analysis.

Figure 2 FT601 FIFO timing diagram

FIFO read (USB out transfer) efficiency calculation:

=Data output / (IDLE + Command Phase + Bus Turn Around + Data output)

For example, if idle cycle is 150 and the FT601 configuration is 1 channel, FIFO depth is 4 KB, then the FIFO read efficiency is (4096/4 (word at FIFO interface))/(2+1+1+4096/4) = 87%

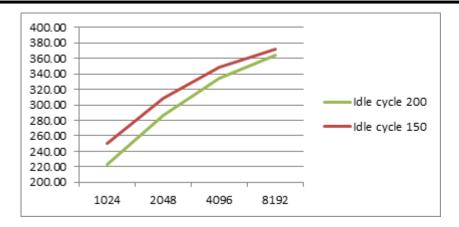

and below give the calculation of FIFO bus data rate when the IDLE time and FT601 FIFO depth vary.

#### Note:

- 1. The idle cycles can either come from the FIFO master when handles the FIFO switching, the FT601 internal configuration and also the USB host transfer speed.

- 2. In multi-channel FIFO mode, the USB host operates individual channels access fairly so that the FIFO master can read or write one channel to another channel with less IDLE cycles. The combined data rate of multiple channels will be higher than the demonstration at single channel only. It also depends on the system performance.

|   |      |     |      | FIFO  |            | Data rate |      |            | Data rate |

|---|------|-----|------|-------|------------|-----------|------|------------|-----------|

|   | Idle | CMD | TURN | depth | Efficiency | (MB/s)    | Idle | Efficiency | (MB/s)    |

| 1 | 150  | 1   | 2    | 1024  | 62.59%     | 250.37    | 200  | 55.77%     | 223.09    |

| 2 | 150  | 1   | 2    | 2048  | 76.99%     | 307.97    | 200  | 71.61%     | 286.43    |

| 3 | 150  | 1   | 2    | 4096  | 87.00%     | 348.00    | 200  | 83.46%     | 333.82    |

| 4 | 150  | 1   | 2    | 8192  | 93.05%     | 372.19    | 200  | 90.98%     | 363.93    |

**Table 2 FIFO efficiency**

Figure 3 FIFO throughput vs FIFO size

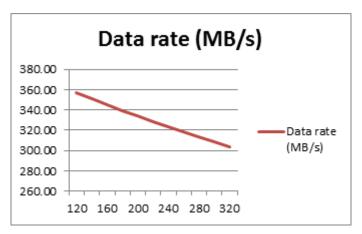

Table 3 and Figure 4 below gives FIFO data rate when the idle period changes.

|    | Idle | CMD | TURN | Efficiency | Data rate (MB/s) |

|----|------|-----|------|------------|------------------|

| 1  | 120  | 1   | 2    | 4096       | 89.28%           |

| 2  | 140  | 1   | 2    | 4096       | 87.75%           |

| 3  | 160  | 1   | 2    | 4096       | 86.27%           |

| 4  | 180  | 1   | 2    | 4096       | 84.84%           |

| 5  | 200  | 1   | 2    | 4096       | 83.46%           |

| 6  | 220  | 1   | 2    | 4096       | 82.12%           |

| 7  | 240  | 1   | 2    | 4096       | 80.82%           |

| 8  | 260  | 1   | 2    | 4096       | 79.56%           |

| 9  | 280  | 1   | 2    | 4096       | 78.35%           |

| 10 | 300  | 1   | 2    | 4096       | 77.17%           |

| 11 | 320  | 1   | 2    | 4096       | 76.02%           |

Table 3 FIFO data rate vs idle cycles in one channel mode (FIFO size is 4 KB)

Figure 4 FIFO data rate vs idle cycles for one channel

#### 2.2.4 Optimize the application and FIFO master design to get the max data rate

From the tables and figures in section 2.2.4, we can observe that if the FIFO master wants to get the max data throughput, the design should consider having a bigger FIFO size and also reduce the idle cycles between FIFO bus data transactions.

There are other things the application needs to take into account, as the USB bulk transfer does not always quaranty the bandwidth, if the application has real time data transfer, e.g. data from data acquisition equipment, the FIFO master should consider to have extra buffer to handle the worst case data rate dip in the transfer.

#### 2.2.5 FT601 data throughput demonstration

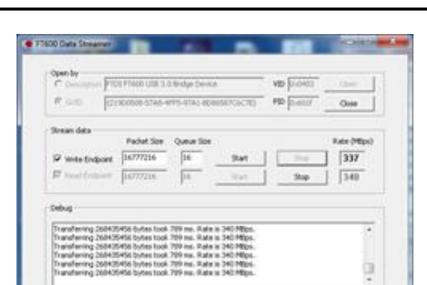

The demonstration is done with the FT600 Data Streamer application. The data rate below is a sustained and effective application data rate, measured when the transfer starts and the full data is collected at the other end.

The following figures are screen captures for the different FT601 configurations. The data is measured for the data transfer on a single channel as a time.

Figure 5 FT601 IN only

Figure 6 FT601 OUT only

Clear Output

Figure 7 FT601 single Channel, IN transfer

Thow Debug Console

Figure 8 FT601 single Channel, OUT transfer

Figure 9 FT601 4 Channels, IN transfer

Figure 10 FT601 4 Channels, OUT transfer

AN\_386 FT600 Maximize Performance

Document Reference No.: FT\_001223 Clearance No.: FTDI# 476

### 3 Conclusion

The combination of several factors determines the best approach to reliable and optimized data flow for a given design. Some designs need a quick response while others require high data throughput. By using the details outlined in this application note, the optimal design can be achieved.

## AN\_386 FT600 Maximize Performance

Document Reference No.: FT\_001223 Clearance No.: FTDI# 476

#### 4 Contact Information

#### Head Office - Glasgow, UK

Future Technology Devices International Limited Unit 1, 2 Seaward Place, Centurion Business Park Glasgow G41 1HH

United Kingdom

Tel: +44 (0) 141 429 2777 Fax: +44 (0) 141 429 2758

E-mail (Sales) sales1@ftdichip.com E-mail (Support) support1@ftdichip.com E-mail (General Enquiries) admin1@ftdichip.com

### Branch Office - Taipei, Taiwan

Future Technology Devices International Limited

(Taiwan)

2F, No. 516, Sec. 1, NeiHu Road

Taipei 114

Taiwan, R.O.C.

Tel: +886 (0) 2 8791 3570 Fax: +886 (0) 2 8791 3576

E-mail (Sales) tw.sales1@ftdichip.com E-mail (Support) tw.support1@ftdichip.com E-mail (General Enquiries) tw.admin1@ftdichip.com

#### Branch Office - Tigard, Oregon, USA

Future Technology Devices International Limited

(USA)

7130 SW Fir Loop Tigard, OR 97223-8160

USA

Tel: +1 (503) 547 0988 Fax: +1 (503) 547 0987

E-Mail (Sales) us.sales@ftdichip.com E-Mail (Support) us.support@ftdichip.com E-Mail (General Enquiries) us.admin@ftdichip.com

#### Branch Office - Shanghai, China

Future Technology Devices International Limited

(China)

Room 1103, No. 666 West Huaihai Road,

Shanghai, 200052

China

Tel: +86 21 62351596 Fax: +86 21 62351595

E-mail (Sales) cn.sales@ftdichip.com E-mail (Support) cn.support@ftdichip.com E-mail (General Enquiries) cn.admin@ftdichip.com

#### **Web Site**

http://ftdichip.com

#### **Distributor and Sales Representatives**

Please visit the Sales Network page of the FTDI Web site for the contact details of our distributor(s) and sales representative(s) in your country.

System and equipment manufacturers and designers are responsible to ensure that their systems, and any Future Technology Devices International Ltd (FTDI) devices incorporated in their systems, meet all applicable safety, regulatory and system-level performance requirements. All application-related information in this document (including application descriptions, suggested FTDI devices and other materials) is provided for reference only. While FTDI has taken care to assure it is accurate, this information is subject to customer confirmation, and FTDI disclaims all liability for system designs and for any applications assistance provided by FTDI. Use of FTDI devices in life support and/or safety applications is entirely at the user's risk, and the user agrees to defend, indemnify and hold harmless FTDI from any and all damages, claims, suits or expense resulting from such use. This document is subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Neither the whole nor any part of the information contained in, or the product described in this document, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. Future Technology Devices International Ltd, Unit 1, 2 Seaward Place, Centurion Business Park, Glasgow G41 1HH, United Kingdom. Scotland Registered Company Number: SC136640

## **Appendix A - References**

#### **Document References**

DS FT600Q-FT601Q IC Datasheet

DS UMFT60xx Module Datasheet

AN 370 FT600 Configuration Programmer User Guide

AN 376 Xilinx FPGA FIFO master Programming Guide

AN 379 D3XX Programmers Guide

AN 385 FTDI D3XX Driver Installation Guide

### **Acronyms and Abbreviations**

| Terms Description |                                                    |  |

|-------------------|----------------------------------------------------|--|

| API               | Application Programming Interface                  |  |

| D3XX              | FTDI Direct Device Driver & API for USB 3.0 bridge |  |

| USB               | Universal Serial Bus                               |  |

| USB-IF            | USB Implementers Forum                             |  |

## Appendix B – List of Tables & Figures

### **List of Tables**

| Table 1 FT600/FT601 mode configuration and FIFO size for each channel         | 4 |

|-------------------------------------------------------------------------------|---|

| Table 2 FIFO efficiency                                                       | 5 |

| Table 3 FIFO data rate vs idle cycles in one channel mode (FIFO size is 4 KB) | e |

| List of Figures                                                               |   |

| Figure 1 performance demo setup diagram                                       | 4 |

| Figure 2 FT601 FIFO timing diagram                                            | 5 |

| Figure 3 FIFO throughput vs FIFO size                                         | 6 |

| Figure 4 FIFO data rate vs idle cycles for one channel                        | e |

| Figure 5 FT601 IN only                                                        | 7 |

| Figure 6 FT601 OUT only                                                       | 7 |

| Figure 7 FT601 single Channel, IN transfer                                    | 8 |

| Figure 8 FT601 single Channel, OUT transfer                                   | 8 |

| Figure 9 FT601 4 Channels, IN transfer                                        | 9 |

| Figure 10 FT601 4 Channels, OUT transfer                                      | 9 |

# Application Note AN\_386 FT600 Maximize Performance

Version 1.0

Document Reference No.: FT\_001223 Clearance No.: FTDI# 476

## **Appendix C - Revision History**

Document Title: AN\_386 FT600 Maximize Performance

Document Reference No.: FT\_001223

Clearance No.: FTDI# 476

Product Page: <a href="http://www.ftdichip.com/FTProducts.htm">http://www.ftdichip.com/FTProducts.htm</a>

Document Feedback: Send Feedback

| Revision | Changes         | Date       |

|----------|-----------------|------------|

| 1.0      | Initial Release | 2015-10-19 |

|          |                 |            |

|          |                 |            |

|          |                 |            |

|          |                 |            |